# NES Console Emulator

Table of Contents

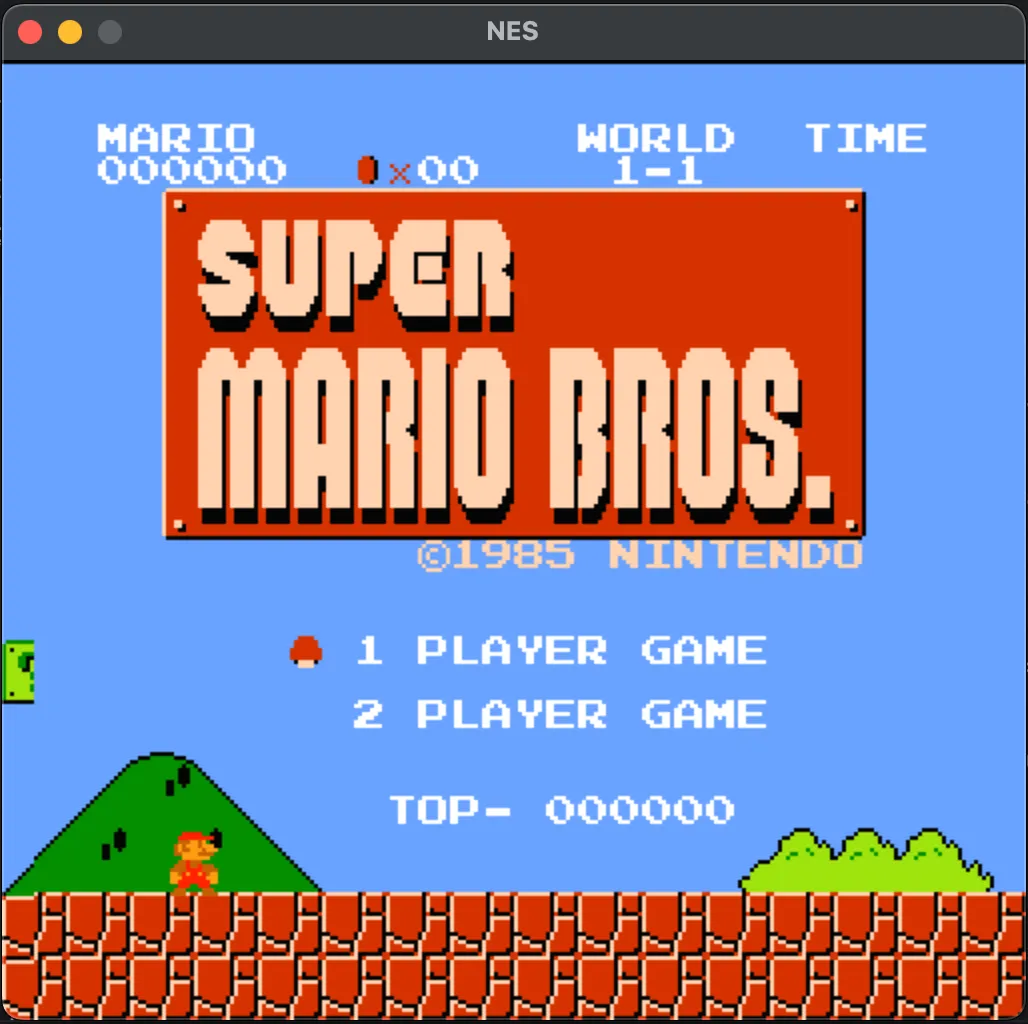

Live Demo

A live demo is available, but not many mappers are supported yet. Improvements are in progress!

Demo here: https://dustinbowers.com/demos/nes-emulator

Goals

- Developing a memory-cycle-accurate NES emulator with cross-platform deployment including WebAssembly

- Implemented complete MOS Technology 6502 CPU instruction set with precise timing emulation

- Architecting PPU (Picture Processing Unit) with per-dot rendering for authentic video output

TODO

- ✅ Implement 6502 CPU (minus APU)

- ✅ Official opcodes

- ✅ Unofficial opcodes

- ✅ Ensure cycle accuracy

- ✅ Create 6502 CPU test runner for single-step tests

- ✅ Implement iNES 1.0 ROM parsing

- ✅ Implement Bus-centric architecture (NES wrapper handles orchestration)

- ✅ Implement interrupt handling

- ✅ Non-maskable-interrupts

- ✅ Software-defined interrupts

- ✅ Implement user-input via Joypad 1

- ✅ Implement cycle-accurate DMA transfer through Bus

- ✅ Implement PPU

- ✅ Background nametable rendering

- ✅ 8x8 sprite rendering (with horiz/vert flips)

- ✅ 8x16 sprite rendering

- ✅ Detect sprite-overflow

- ✅ Sprite collision detection

- ✅ Fix buggy scrolling

- ✅ Encapsulate mapper logic behind Cartridge trait

- ✅ Implement APU

- ✅ Pulse Channels

- ✅ Noise Channel

- ✅ Triangle Channel

- ✅ DMC DMA

- ✅ DPCM Channel

Implementing the 6502 CPU

Implementing the MOS 6502 CPU is naturally a foundational step in building a NES emulator. While CPU emulation always involves a series of predictable, albeit meticulous, tasks, the 6502 presented a unique challenge: its diverse array of addressing modes. These modes dictate how an instruction locates its operand in memory, and decoupling this addressing logic from each instruction’s core operation was my primary goal for a maintainable and scalable design.

I’ve detailed the general approach I took to solve this in a dedicated blog post: Simplifying 6502 Addressing Modes in Rust Emulation.

Implementing the PPU

[TODO]

Resources

- 6502 opcode references:

- Illegal opcodes

- Single-step opcode tests

- iNES file format spec

- snake.nes

- PPU timing: